# Lyles College of Engineering Department of Electrical and Computer Engineering

# **Technical Report**

| <b>Experiment Title:</b> | 5-Stage Pipelined MIPS Processor       |

|--------------------------|----------------------------------------|

| <b>Course Title:</b>     | ECE 174 Advanced Computer Architecture |

| Instructor:              | Dr. Hayssam El-Razouk                  |

| <b>Date Submitted:</b>   | 18 May, 2023                           |

# **Prepared By:**

Sections Written:

Puya Fard

Section 1, 2, 3, 4, 5, 6

Carlos Lopez

# **INSTRUCTOR SECTION**

# **Comments:**

Final Grade:Team Member 1:Puya FardTeam Member 2:Carlos Lopez

# **TABLE OF CONTENTS**

| Secti | on |

|-------|----|

| Secu  | on |

| TITL | PAGE                                                                                  | 1  |

|------|---------------------------------------------------------------------------------------|----|

| TABI | OF CONTENTS                                                                           | 2  |

| 1.   | STATEMENT OF OBJECTIVES                                                               | 3  |

| 2.   | THEORETICAL BACKGROUND                                                                | 3  |

| 3.   | EXPERIMENTAL PROCEDURE.                                                               | 18 |

|      | 3.1. Equipment Used                                                                   | 18 |

|      | 3.2. Project Procedure Description                                                    | 18 |

|      | 3.2.1. Task 1: Implementation of individual blocks for single-cycle MIPS Processor    | 18 |

|      | 3.2.2. Task 2: Implementation of Forwarding logic to transform into                   | 19 |

|      | 3.2.3. Task 3: Implementation of Hazard Control unit to detect any                    |    |

|      |                                                                                       | 19 |

|      |                                                                                       | 19 |

|      | 3.3. Procedure Execution                                                              | 20 |

|      | 3.3.1. Task 1: Implementation of individual blocks for single-cycle MIPS<br>Processor | 20 |

|      | 3.3.2. Task 2: Implementation of Forwarding logic to transform into pipeline logic.   | 37 |

|      | 3.3.3. Task 3: Implementation of Hazard Control unit to detect any                    |    |

|      |                                                                                       | 53 |

|      |                                                                                       | 56 |

| 4.   |                                                                                       | 57 |

|      | 4.1. Experimental Results                                                             | 57 |

|      |                                                                                       | 86 |

|      |                                                                                       | 90 |

| 5.   |                                                                                       | 93 |

| 6.   | REFERENCES                                                                            | 94 |

### **1. STATEMENT OF OBJECTIVES**

The objective of this project is to integrate and prototype the datapath and the control units of the simple 32-bit MIPS processor with five pipeline stages. This processor should be written in Verilog hardware language and must be able to perform arithmetic/logic, data movement, and flow control instructions. Furthermore, students should design and architect the memory to support the following zones: code section and data section. Finally, having the processor operate on an Intel DE2-115 FPGA development board is the ultimate goal of this project. The learning outcomes of this project will result in students having hands- on experience on building a computer processor and implementing it on hardware.

### 2. THEORETICAL BACKGROUND

### Modelsim - source: ("ModelSim HDL simulator | Siemens Software")

ModelSim is a hardware simulation and debugging tool developed by Mentor Graphics, which is used for designing and testing digital circuits. It is one of the most widely used simulation tools in the industry and is often used in the development of electronic systems, ranging from simple digital circuits to complex integrated circuits (ICs) and system-on-chip (SoC) designs.

ModelSim supports both Verilog and VHDL hardware description languages (HDLs), which are used to describe the behavior of digital circuits. HDLs are programming languages that allow designers to describe the function and behavior of a digital circuit, including its inputs, outputs, and internal workings, in a way that can be simulated and tested.

ModelSim uses a powerful simulation engine that can simulate millions of logic gates and thousands of flip-flops in a matter of seconds. It allows designers to simulate and test their designs before they are physically implemented, which can help to catch errors and reduce the time and cost of development.

In addition to simulation, ModelSim also provides advanced debugging features, such as waveform viewing and tracing, which allow designers to visualize and analyze the behavior of their designs. It also includes support for advanced verification methodologies such as Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

## MIPS Implementation - source: (<u>https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml</u>)

Before looking at the diagram we need a little bit of context:

A very brief introduction to logic circuits. A very high-level view of the processor's datapath. A quick overview of some intermediate-level processor organizations. The single-cycle organization is one of these organizations.

After looking at the diagram we will:

Look at black-box descriptions of the components of the diagram. Take a quick look at the functions of control signals in the diagram.

Logic Circuits: Logic circuits use two different values of a physical quantity, usually voltage, to represent the boolean values true (or 1) and false (or 0). Logic circuits can have inputs and they have one or more outputs that are, at least partially, dependent on their inputs. In logic circuit diagrams, connections from one circuit's output to another circuit's input are often shown with an arrowhead at the input end.

In terms of their behavior, logic circuits are much like programming language functions or methods. Their inputs are analogous to function parameters and their outputs are analogous to function returned values. However, a logic circuit can have multiple outputs.

There are two basic types of logic circuitry: combinational circuits and state circuits.

- Combinational circuit behaves like a simple function. The output of a combinational circuit depends only on the current values of its input.

- State circuitry behaves more like an object method. The output of state circuitry does not just depend on its inputs it also depends on the past history of its inputs. In other words, the circuitry has memory.

This is much like an object method whose value is dependent on the object's state: its instance variables. These two types of circuitry work together to make up a processor datapath.

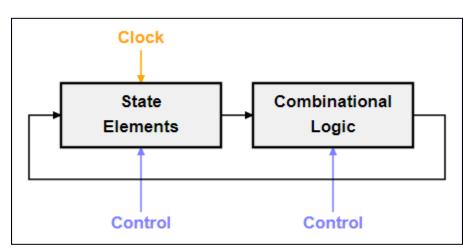

Processor Datapath:

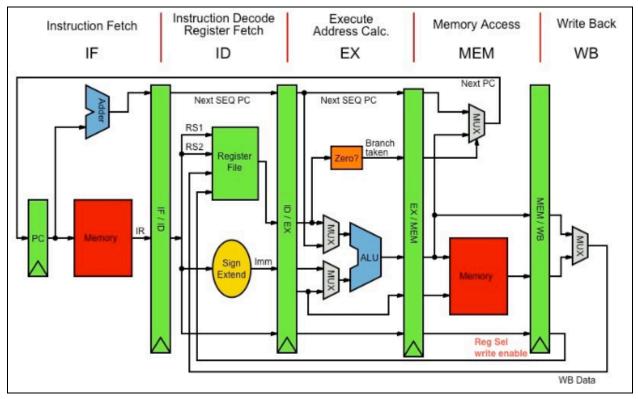

Figure 2.1: Processor datapath

A processor's datapath is conceptually organized into two parts:

- State elements hold information about the state of the processor during the current clock cycle. All registers are state elements.

- Combinational logic determines the state of the processor for the next clock cycle. The ALU is combinational logic.

This diagram, like most diagrams on this web site, adheres to the following conventions:

- Clock signals are colored orange.

- Control signals are colored blue.

There are four major processor organizations:

- Single-cycle organization: This is the organization described in this web presentation. It is characterized by the fact that each instruction is executed in a single clock cycle. It is not a realistic implementation it requires two separate memories: one for data and one for instructions. Also, the clock cycle has to be made quite long in order for all of the signals generated in a cycle to reach stable values.

- Multicycle organization: This organization uses multiple clock cycles for executing each instruction. Each cycle does only a small part of the work required so the cycles are much shorter. Much of the circuitry is the same as the single-cycle implementation. However, more state components must be added to hold data that is generated in an early cycle but used in a later cycle.

- Pipelined organization: Like the multicycle organization, the pipelined organization uses multiple clock cycles for executing each instruction. By adding more state components for passing data and control signals between cycles, the pipelined organization turns the circuitry into an assembly line. After the first cycle of one instruction has completed you can start the execution of another instruction, while the first moves to its next cycle. Several instructions can be in different phases of execution at the same time.

- Register renaming organization: Register renaming is an extension of the pipelining idea. It deals with the data dependence problem for a pipeline — the fact that instructions in the pipeline produce data needed by other instructions in the pipeline.

# Pipelining - source: (<u>https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml</u>)

The basic concept of pipelining is to break up instruction execution activities into stages that can operate independently. Every instruction passes through the same stages much like an assembly line.

For example, we could set up the following stages for a MIPS pipeline.

- IF instruction fetch and PC increment

- ID source register fetch and instruction decode

- EX ALU source selection, ALU operation, and branch target calculation

- MEM data memory access

- WB write back to destination register

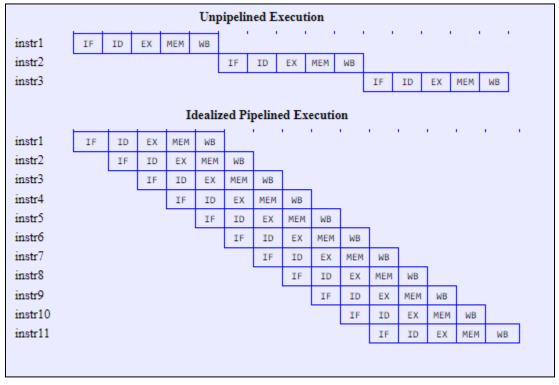

With these pipeline stages, a sequence of instructions can be executed as shown below. Time progresses from left to right. Each horizontal division represents one clock period.

|       |                  | <b>—</b> | -  | -  | -   |     | 1   |     |     |     | 1  | 1.0 |

|-------|------------------|----------|----|----|-----|-----|-----|-----|-----|-----|----|-----|

| 1.s   | \$f0, 0(\$t1)    | IF       | ID | EX | MEM | WB  |     |     |     |     |    |     |

| 1.s   | \$f2, 0(\$t2)    |          | IF | ID | EX  | MEM | WB  |     |     |     |    |     |

| mul.s | \$f4, \$f0, \$f2 |          |    | IF | ID  | EX  | MEM | WB  |     |     |    |     |

| add.s | \$f6, \$f6, \$f4 |          |    |    | IF  | ID  | EX  | МЕМ | WB  |     |    |     |

| addi  | \$t1, \$t1, 4    |          |    |    |     | IF  | ID  | EX  | MEM | WB  |    |     |

| addi  | \$t2, \$t2, 4    |          |    |    |     |     | IF  | ID  | EX  | MEM | WB |     |

|       |                  |          |    |    |     |     |     |     |     |     |    | -   |

Figure 2.2: Pipeline stages

## Benefit of Pipelining - source: (<u>https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml</u>)

As you can see from the figures below, pipelining increases instruction throughput. Notice that after the 5th cycle, the unpipelined execution completes only one instruction every 5 cycles, while the idealized pipelined execution completes 5.

Ideally, instruction throughput is increased to 1 instruction per clock. In other words, the clocks per instruction (CPI) factor in the performance equation is reduced from 5.0 to 1.0.

Figure 2.3: Pipeline benefits

# Pipeline Implementation - source: (<u>https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml</u>)

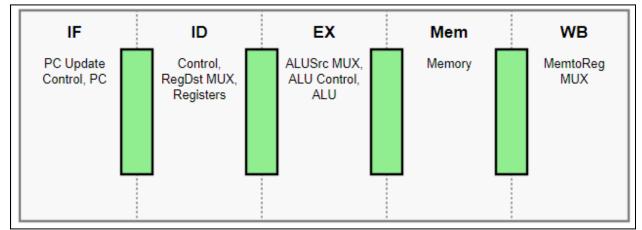

The best starting point for a pipelined implementation is a single-cycle implementation. For example, for a MIPS pipeline you could start with an implementation whose high-level data path is shown as the "Before Pipelining" diagram below.

| IF                       | ID                                   | EX                                 | Mem    | WB              |

|--------------------------|--------------------------------------|------------------------------------|--------|-----------------|

| PC Update<br>Control, PC | Control,<br>RegDst MUX,<br>Registers | ALUSrc MUX,<br>ALU Control,<br>ALU | Memory | MemtoReg<br>MUX |

Figure 2.4: Before pipeline implementation

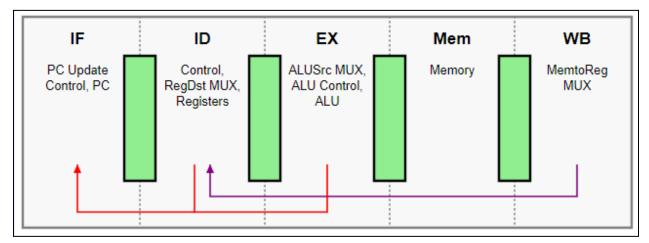

To implement pipelining registers are added between stages. The pipelining registers are shown in light green in the "After Pipelining" diagram below. The pipelining registers hold data and control signals that are produced in an early stage for use in later stages.

Signals generated in a stage cannot be held for more than one cycle. A signal that is generated in an early stage and used several stages later must pass through all of the intermediate pipeline registers. For example, a control signal that is produced in the ID stage and used in the WB stage must pass through 3 pipelining registers: the ID/EX registers, the EX/MEM registers, and the MEM/WB registers.

Figure 2.5: After pipeline implementation

# Obstacles to Pipelining - source: (https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml)

The analogy between a pipeline and an assembly line breaks down in one important respect. Putting together a door for a car does not depend on cars further along in the assembly line.

But there are dependencies between instructions. These can be seen in the diagram below where data is passed back from a later stage to an earlier stage. The ones that involve updating the PC (red) are called control hazards. The ones that involve writing data back to registers (purple) are called data hazards.

Both of these dependencies are inherent in the instruction set. Compiler writers call them control and data dependencies. In both cases the execution of a later instruction depends on the results of earlier instruction. There are other obstacles, called structural hazards that arise from the starting point of the pipelining implementation

Figure 2.6: Dependencies

# Control Hazards - source: (https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml)

Control hazards arise from branches and jumps. They involve signals that are passed from a later stage to an earlier stage:

- A branch or jump target address is not available until the ID stage but it needs to be passed back to the PC for the IF stage of the next instruction.

- The condition for a branch instruction is not tested until the EX stage but it needs to be passed back to the PC Update Control for the IF stage of the next instruction.

### Data Hazards - source: (https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml)

Data hazards arise from instructions producing data that is used in later instructions. They involve signals that are selected by the MemtoReg multiplexer in the WB stage to be written to a register. The register may be read by a later instruction in its ID stage.

### Structural Hazards - source: (https://www.d.umn.edu/~gshute/mips/mips-intro.xhtml)

Structural hazards are hazards that depend on the starting point for the implementation. For example, if we started with a multicycle implementation, we would have problems in a pipeline because the ALU is used in more than one stage by the same instruction. Executing a branch instruction, the ALU is used to increment the PC, compute a branch target address, and compare two source operands. These uses are going to prevent other instructions in the pipeline from using the ALU.

### Pipelining and the Instruction Set

Pipelining is one of the primary reasons why RISC processors have a significant speed advantage over CISC processors. If arithmetic and logical instructions can access memory for source or destination operands then it is much more difficult to break down instruction execution into stages with equal durations. If memory addressing modes are complex then this problem just gets harder. If instructions have varying lengths it is more difficult to start a new instruction every cycle.

When pipelining is done with a CISC processor it is done at a different level. The execution of instructions is broken down into smaller parts which can then be pipelined. In effect, The CISC instructions are translated into a sequence of internal RISC instructions, which are then pipelined. This adds complexity to the processor and generally does not produce as much benefit. For upward compatibility, the Intel 80x86 family of processors, including Pentium processors since the early 1990s, have used this approach.

5-Stage-Pipeline MIPS - source: ("VHDL MIPS 5 stage pipeline Bug")

Figure 2.7: 5-stage pipeline for MIPS

The figure above **Figure 2.7** shows the complete 5 stages required for the 32-bit mips processor. The figure isn't a complete list of requirements for completing the processor, muxes, control units, and hazard block isn't displayed. However, it is a general idea for completing the processor.

# Understanding Mips Instructions - source: ("VHDL MIPS 5 stage pipeline Bug")

Data types:

- 1. Instructions are all 32 bits

- 2. byte(8 bits), halfword (2 bytes), word (4 bytes)

- 3. a character requires 1 byte of storage

- 4. an integer requires 1 word (4 bytes) of storage

Registers

- 32 general-purpose registers

- register preceded by \$ in assembly language instruction

- two formats for addressing:

- using register number e.g. \$0 through \$31

- using equivalent names e.g. \$t1, \$sp

- special registers Lo and Hi used to store result of multiplication and division

- not directly addressable; contents accessed with special instruction mfhi ("move from Hi") and mflo ("move from Lo")

| Register<br>Number | Alternative<br>Name | Description                                                                                                                                                        |

|--------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | zero                | the value 0                                                                                                                                                        |

| 1                  | \$at                | (assembler temporary) reserved by the assembler                                                                                                                    |

| 2-3                | \$v0 - \$v1         | (values) from expression evaluation and function results                                                                                                           |

| 4-7                | \$a0 - \$a3         | (arguments) First four parameters for subroutine.<br>Not preserved across procedure calls                                                                          |

| 8-15               | \$t0 - \$t7         | (temporaries) Caller saved if needed. Subroutines can use w/out<br>saving.<br>Not preserved across procedure calls                                                 |

| 16-23              | \$s0 - \$s7         | (saved values) - Callee saved.<br>A subroutine using one of these must save original and restore it before exiting.<br>Preserved across procedure calls            |

| 24-25              | \$t8 - \$t9         | (temporaries) Caller saved if needed. Subroutines can use w/out<br>saving.<br>These are in addition to \$t0 - \$t7 above.<br>Not preserved across procedure calls. |

| 26-27              | \$k0 - \$k1         | reserved for use by the interrupt/trap handler                                                                                                                     |

| 28                 | Sgp                 | global pointer.<br>Points to the middle of the 64K block of memory in the static data<br>segment.                                                                  |

| 29                 | \$sp                | stack pointer<br>Points to last location on the stack.                                                                                                             |

| 30                 | \$s8/\$fp           | saved value / frame pointer<br>Preserved across procedure calls                                                                                                    |

| 31                 | \$ra                | return address                                                                                                                                                     |

• stack grows from high memory to low memory

Figure 2.8: Register descriptions

### Program Structure - source: ("VHDL MIPS 5 stage pipeline Bug")

- just plain text file with data declarations, program code (name of file should end in suffix .s to be used with SPIM simulator)

- data declaration section followed by program code section

Data Declarations

- placed in section of program identified with assembler directive .data

- declares variable names used in program; storage allocated in main memory (RAM)

### Code

- placed in section of text identified with assembler directive .text

- contains program code (instructions)

- starting point for code execution given label main:

- ending point of main code should use exit system call (see below under System Calls)

### Comments

- anything following # on a line

- # This stuff would be considered a comment

### Load / Store Instructions - source: (Lecture slides)

RAM access is only allowed with load and store instructions. all other instructions use register operands.

| <u>load:</u>    |                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| lw              | register_destination, RAM_source                                                                                        |

|                 | #copy word (4 bytes) at source RAM location to destination register.                                                    |

| 16              | register_destination, RAM_source                                                                                        |

|                 | #copy byte at source RAM location to low-order byte of destination register,<br># and sign-extend to higher-order bytes |

| store word:     |                                                                                                                         |

| 510             | register_source, RAM_destination                                                                                        |

|                 | #store word in source register into RAM destination                                                                     |

| sb              | register_source, RAM_destination                                                                                        |

|                 | #store byte (low-order) in source register into RAM destination                                                         |

| load immediate: |                                                                                                                         |

| li              | register_destination, value                                                                                             |

|                 | #load immediate value into destination register                                                                         |

Figure 2.9: lw/sw instructions

# **Arithmetic Instructions**

- most use 3 operands

- all operands are registers; no RAM or indirect addressing

- operand size is word (4 bytes)

```

add

add as signed (2's complement) integers

$t0,$t1,$t2

# $t0 = $t1 + $t2;

# $t2 = $t3 Đ $t4

sub

$t2,$t3,$t4

# $t2 = $t3 + 5; "add immediate" (no sub immediate)

$t2,$t3, 5

addi

addu

$t1,$t6,$t7

#

t1 = t6 + t7;

add as unsigned integers

$t1,$t6,$t7

# $t1 = $t6 + $t7;

subtract as unsigned integers

subu

mult

$t3,$t4

# multiply 32-bit quantities in $t3 and $t4, and store 64-bit

# result in special registers Lo and Hi: (Hi,Lo) = $t3 * $t4

div

$t5,$t6

# Lo = $t5 / $t6

(integer quotient)

# Hi = $t5 mod $t6

(remainder)

mfhi

# move quantity in special register Hi to $t0:

$t0

$t0 = Hi

# move quantity in special register Lo to $t1:

$t1 = Lo

mflo

$t1

# used to get at result of product or quotient

move

$t2,$t3 # $t2 = $t3

```

Figure 2.10: Arithmetic operations

#### **Control Structures**

Branches: comparison for conditional branches is built into instruction

| b   | target                      | # | unconditional branch to program label target |

|-----|-----------------------------|---|----------------------------------------------|

| beq | <pre>\$t0,\$t1,target</pre> | # | branch to target if \$t0 = \$t1              |

| blt | \$t0,\$t1,target            | # | branch to target if \$t0 < \$t1              |

| ble | \$t0,\$t1,target            | # | branch to target if \$t0 <= \$t1             |

| bgt | <pre>\$t0,\$t1,target</pre> | # | branch to target if \$t0 > \$t1              |

| bge | \$t0,\$t1,target            | # | branch to target if \$t0 >= \$t1             |

| bne | \$t0,\$t1,target            | # | branch to target if \$t0 <> \$t1             |

Figure 2.11: Control operations

Jumps

```

j target # unconditional jump to program label target

jr $t3 # jump to address contained in $t3 ("jump register")

```

Figure 2.12: Control operations 2

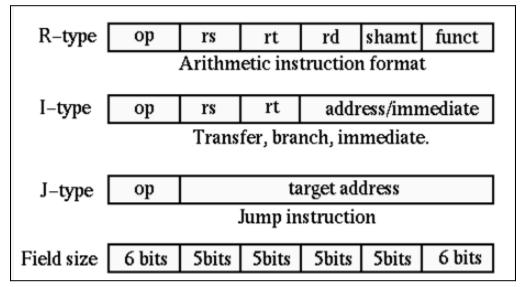

#### **MIPS Instruction Types - source: (Lecture notes)**

When MIPS instructions are classified according to coding format, they fall into four categories: R-type, J-type, J-type, and coprocessor. The coprocessor instructions are not considered here.

The classification below refines the classification according to coding format, taking into account the way that the various instruction fields are used in the instruction. The details of the execution activities and the required control signal values depend almost entirely on the instruction type in this classification.

- Non-Jump R-Type

- Immediate Arithmetic and Logic

- Branch

- Load

- Store

- Non-Register Jump

- Register Jump

In the remainder of this web page, the instruction fetch and instruction decode activities are omitted since they are the same for all instructions. The PC update activity only shows updates beyond the standard PC increment (PC  $\leftarrow$  PC + 4).

Figure 2.12: Instruction information

# Non-Jump R-Type

Non-jump R-type instructions include all R-type instructions except jr and jalr. This includes all of the integer arithmetic and bitwise operations, along with the non-branching compare instructions such as slt, sgt, and seq. They use the R coding format. The opcode bits are all 0.

- PC update: There is no update beyond the normal increment.

- Source operand fetch: The two source operands are rs and rt.

- ALU operation: The ALU operation is determined by the function field.

- Memory access: There is no memory access for data.

- Register write: The result from the ALU is written to rd.

### **Immediate Operand**

Most immediate operand instructions perform arithmetic or logical operations using one operand that is coded into the instruction. The immediate operand group also includes the comparison instructions slti and sltiu and the lui instruction. Immediate operand instructions use the I coding format.

- PC update: There is no update beyond the normal increment.

- Source operand fetch: The two source operands are rs and the immediate field. For all instructions except sltiu the immediate field is sign extended. For sltiu the immediate field is zero extended. This instruction is not considered in Patterson and Hennessey.

- ALU operation: The ALU operation is determined by the opcode.

- Memory access: There is no memory access for data.

- Register write: The result from the ALU is written to rt.

### Branch

Branch instructions conditionally branch to an address whose distance is coded into the instruction. Branch instructions use the I coding format.

- PC update: If the branch condition is true (see ALU operation), PC ← PC + 4 + (sign-extended immediate field)<<2.

- Source operand fetch: The two source operands are rs and rt.

- ALU operation: The source operands are subtracted for comparison.

- Memory access: There is no memory access for data.

- Register write: There is no register write.

### **3. EXPERIMENTAL PROCEDURE**

### 3.1 Equipment used

- 1. Personal Computer

- 2. Modelsim

- 3. Lecture slides and ICAs

### 4. Online resources

### **3.2 Project Procedure Description**

### 3.2.1. Task 1: Implementation of individual blocks for single-cycle MIPS processor

- 1. When it comes to designing a MIPS processor, it's always good to start off with individual blocks required rather than trying to implement it all together.

- 2. The first glance of implementation on the MIPS processor is focused on the single cycle because it is easier to debug if there are any errors in individual blocks at the beginning.

- 3. Therefore, the processor is divided into small modules as follows:

- a. ALU

- b. ALU\_Control

- c. Branch\_Adder

- d. Control\_Unit

- e. Data\_Memory

- f. Instruction\_Memory

- g. Jump\_Calc

- h. Program\_Counter

- i. Register\_File

- j. Sign Extend

- k. Mux

- i. Operand\_mux

- ii. Pc\_mux

- iii. Reg\_file\_mux

- iv. Write\_back\_mux

- 1. Processor\_top: which is the top module to connect all the modules for single-cycle MIPS Processor.

- 4. Once all the modules are connected via the top module, there will be simulations that will be analyzed to check if there are any errors with individual modules before moving to the next stage of the process, forwarding and pipelining.

### **3.2.2.** Task 2: Implementation of Forwarding logic to transform into pipeline logic

- 1. Once configured the single-cycle MIPS processor from task 1, we will go ahead and implement the forwarding logic by implementing the following modules:

- a. IFID

- b. IDEX

- c. EXMEM

- d. MEMWB

- 2. Once these modules are completed, then we will configure the processor\_top module accordingly to use these blocks for forwarding logic.

- 3. Once done, simulate the results and check if there are any errors in individual modules and overall wave outputs.

### 3.2.3. Task 3: Implementation of Hazard Control unit to detect any hazards

- 1. As mentioned under the theoretical section of this report, while doing forwarding, we will encounter hazards along the way.

- 2. Therefore, in this step of the project, we have implemented hazard control module to detect any hazard found

- 3. If it does, then we will generate "bubbles" to make sure pipelining is successfully operating with no problem.

### 3.2.4. Task 4: Simulations

- 1. Once at this stage, the 5-stage pipelined MIPS processor design is complete

- 2. Now we are doing simulations and testing the instructions listed in the project manual to see if we are getting correct results and our processor is doing what we want.

- 3. The findings for this step will be under the Analysis section.

### 3.2.5. Task 5: Implementation of the processor on FPGA

- 1. At this stage of the project, we will upload the processor onto the FPGA, specifically the DE2-115 development board.

- 2. We will test our instructions one by one and check our results

- 3. It must be noted that we will use FPGAs memory instead of registers while testing our processor.

### **3.3 Project Execution**

### 3.3.1. Task 1: Implementation of individual blocks for single-cycle MIPS processor

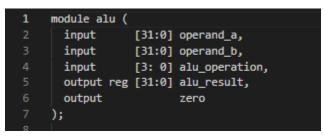

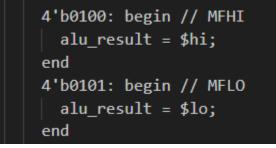

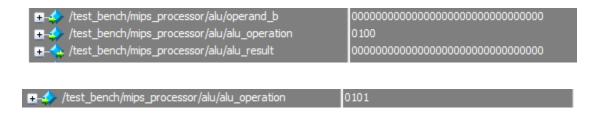

**ALU:** ALU stands for Arithmetic Logic Unit, which is a fundamental component of a computer's central processing unit (CPU). The ALU is responsible for performing arithmetic and logical operations on binary numbers.

The arithmetic operations include addition, subtraction, multiplication, and division, while the logical operations include AND, OR, NOT, and XOR. The ALU can perform these operations on single bits or on groups of bits, depending on the instruction provided to it by the CPU.

The ALU has inputs for two binary numbers and a control signal that determines the operation to be performed on the numbers. It then performs the operation and outputs the result. The result can be used by other components of the CPU or stored in memory.

Now let's take a look at the ALU Module that is implemented for this project:

### Figure 3.3.1: Initialize

We first must initialize our input, output and output reg ports just like given above, responsible for being a placeholder for operand a, b and output. Then we will start initializing our arithmetic and logical operations one by one with a case number assigned to them.

```

// Calculate the multiplication result

assign mult_result = operand_a * operand_b;

// perform the ALU operation based on the ALU control signal

always @* begin

case (alu_operation)

4'b0000: begin // And

alu_result = operand_a & operand_b;

end

4'b0001: begin // Or

alu_result = operand_a | operand_b;

end

4'b0010: begin // Add, ADDI, LW, SW

alu_result = operand_a + operand_b;

end

```

### Figure 3.3.2: Cases

After initialization of each individual case that has a corresponding arithmetic, logic, or data flow operation, our ALU module is completed. However, we still need to configure the control module that will interact with the ALU module.

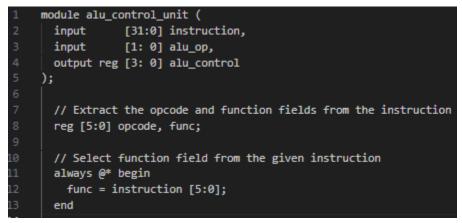

**ALU CONTROL:** The ALU Control Unit (ALU CU) is responsible for controlling the operation of the Arithmetic Logic Unit (ALU) within a CPU. The ALU CU takes in the instruction from the CPU, which specifies the type of arithmetic or logical operation that needs to be performed on the data.

The ALU CU is responsible for generating the appropriate control signals that direct the ALU to perform the correct operation. It determines which arithmetic or logical operation needs to be performed, based on the instruction provided, and generates the appropriate signals to control the ALU's operation.

The ALU CU is also responsible for deciding how the result of the operation should be handled, including setting the appropriate condition codes to indicate whether the result is negative, zero, or positive.

Figure 3.3.3: Initialize

The module takes in an instruction and an ALU operation code as input and produces a 4-bit output signal called alu\_control, which specifies the operation to be performed by the Arithmetic Logic Unit (ALU).

The code first extracts the opcode and function fields from the instruction. The opcode is a 6-bit field that specifies the type of instruction, and the function field is a 6-bit field that specifies the specific operation to be performed by the ALU for R-Type instructions.

The module then uses a case statement to determine the appropriate value for alu\_control based on the input instruction and alu\_op. The case statement handles three cases based on the value of alu\_op:

Finally, the module outputs the value of alu\_control, which is used to control the operation of the ALU. The value of alu\_control specifies the specific operation to be performed by the ALU, such as addition, subtraction, multiplication, or logical operations like AND, OR, and NOR.

```

// Control signals for R, I and J-TYPE instructions

always @* begin

case (alu_op)

2'b00: begin

// I and J-Type

case (instruction[31:26]) // Checking opcode for I-Type instructions as they don't have the function field

6'b001000: begin // ADDI

alu_control = 4'b0010;

end

6'b100011: begin // LW

alu_control = 4'b0010;

end

6'b101011: begin // SW

alu_control = 4'b0010;

end

default: alu_control = 4'b1111; // NOP

endcase

end

2'b01: begin

alu_control = 4'b0110; // BEQ

2'b10: begin

case (func)

6'b100000: begin // Add

alu_control = 4'b0010;

end

6'b100010: begin // Subtract

alu_control = 4'b0110;

end

6'b100100: begin // And

alu_control = 4'b0000;

end

6'b100101: begin // Or

alu_control = 4'b0001;

end

6'b101010: begin // Set on less than

alu_control = 4'b0111;

end

6'b100111: begin // Nor

alu_control = 4'b1000;

end

6'b011010: begin // Div

alu_control = 4'b1010;

end

6'b011000: begin // Mult

alu_control = 4'b1011;

end

6'b010000: begin // Mfhi

alu_control = 4'b0100;

end

6'b010010: begin // Mflo

alu_control = 4'b0101;

end

endcase

end

2'b11: begin

alu_control = 4'b0;

```

Figure 3.3.4: Control signals for R, I and J-TYPE instructions

**BRANCH ADDER:** The "branch\_adder" module performs a critical function in a processor's pipeline to calculate the address of the next instruction after a branch instruction is executed. This module is used in conjunction with other components of a processor's pipeline to ensure correct execution of branch instructions.

| 1  | module branch_adder (                                          |

|----|----------------------------------------------------------------|

| 2  | input branch,                                                  |

| 3  | input [31:0] current_pc,                                       |

| 4  | input [31:0] sign_extend,                                      |

| 5  | output reg [31:0] pc_branch                                    |

| 6  | );                                                             |

| 7  |                                                                |

| 8  | <pre>// Calculate the address for the branch</pre>             |

| 9  | always @* begin                                                |

| 10 | <pre>pc_branch = branch ? current_pc + sign_extend : '0;</pre> |

| 11 | end                                                            |

| 12 |                                                                |

| 13 | endmodule                                                      |

|    |                                                                |

Figure 3.3.5: Branch adder

The module takes in three input signals: "branch", "current\_pc", and "sign\_extend", and produces an output signal "pc\_branch", which is the address of the next instruction to be executed after a branch instruction is encountered.

The "branch" signal is a single bit that indicates whether a branch is being taken or not. The "current\_pc" signal is a 32-bit input that represents the current program counter (PC), which is the address of the current instruction being executed. The "sign\_extend" signal is a 32-bit input that represents the sign-extended immediate value of the branch instruction.

The module uses an "always" block to calculate the address of the next instruction after a branch. If "branch" is high, indicating that a branch is being taken, the module adds the "sign\_extend" value to the "current\_pc" value to calculate the address of the next instruction. If "branch" is low, indicating that a branch is not being taken, the module sets the "pc branch" value to '0'.

The output signal "pc\_branch" is a 32-bit value that represents the address of the next instruction to be executed after a branch. If the branch is taken, the value of "pc\_branch" will be equal to "current\_pc" plus the "sign\_extend" value. If the branch is not taken, the value of "pc\_branch" will be 0.

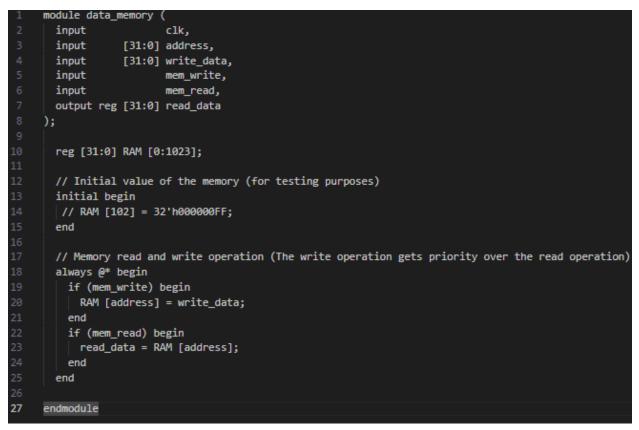

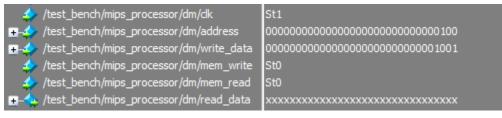

**DATA MEMORY:** This module essentially implements a simple memory unit where data can be written to or read from specific memory locations based on an address input.

Figure 3.3.6: Data memory

This code defines a module for a data memory unit in a digital system. The module has a synchronous interface consisting of an address input (address), a write data input (write\_data), and read/write control signals (mem\_read and mem\_write) that are triggered by a clock signal (clk). The module also has an output read\_data which represents the data read from the memory location specified by the address input.

The module implements the memory using an array of 1024 32-bit registers (RAM), initialized to zero. The address input is used to index the RAM array to perform memory read or write operations. When mem\_write is asserted, the write\_data input is written to the memory location specified by the address input. When mem\_read is asserted, the read\_data output is updated with the data stored in the memory location specified by the address input.

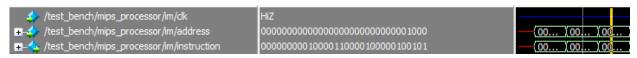

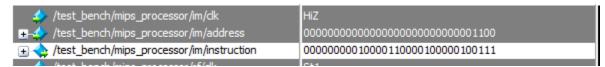

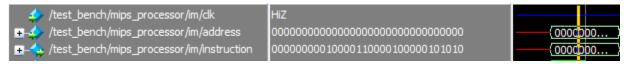

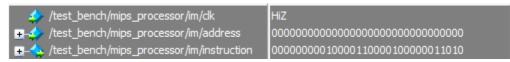

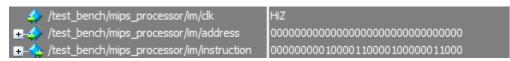

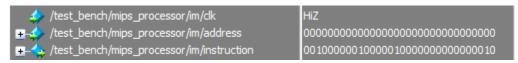

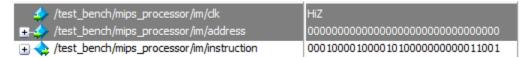

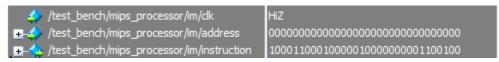

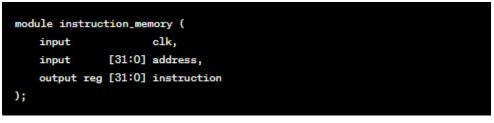

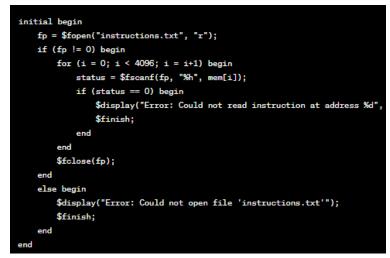

**INSTRUCTION MEMORY:** The instruction\_memory module provides an interface for a processor to read instructions from a memory based on a specified address.

```

module instruction_memory (

// clock input (active-high)

input

clk,

[31:0] address,

input

output reg [31:0] instruction

reg [7:0] mem[0:4095];

initial begin

// R-TYPE

= 32'h00430820; // add

{mem[3 ],mem[2 ],mem[1 ],mem[0 ]}

= 32'h00430824; // and

= 32'h00430825; // or

{mem[7 ],mem[6 ],mem[5 ],mem[4 ]}

{mem[11],mem[10],mem[9 ],mem[8 ]}

= 32'h00430827; // nor

{mem[15],mem[14],mem[13],mem[12]}

= 32'h00430822; // sub

{mem[19],mem[18],mem[17],mem[16]}

= 32'h0043082A; // slt

= 32'h0043081A; // div

{mem[23],mem[22],mem[21],mem[20]}

{mem[27],mem[26],mem[25],mem[24]}

= 32'h00430818; // mul

{mem[31],mem[30],mem[29],mem[28]}

= 32'h00000810; // mfhi

{mem[35],mem[34],mem[33],mem[32]}

{mem[39],mem[38],mem[37],mem[36]}

= 32'h00000812; // mflo

// I-Type

{mem[43],mem[42],mem[41],mem[40]}

= 32'h20410003; // addi

= 32'h10850019; // beq

{mem[47],mem[46],mem[45],mem[44]}

{mem[51],mem[50],mem[49],mem[48]}

32'h8c410064; // lw

{mem[55],mem[54],mem[53],mem[52]}

= 32'hAC410064; // sw

// J-Type

{mem[59],mem[58],mem[57],mem[56]} = 32'h08000101; // j

end

always @* begin

instruction = {mem[address+3], mem[address+2], mem[address+0]};

end

endmodule

```

Figure 3.3.7: Instructions

The instruction\_memory module is a memory unit that stores instructions for a processor. It has three inputs:

- 1. clk: a clock signal

- 2. address: a 32-bit input representing the memory address to read from

- 3. instruction: a 32-bit output representing the instruction read from the memory

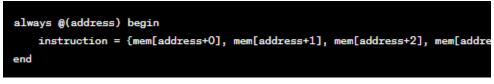

The module uses a reg array called mem to store the instructions. The initial values of this array are set in the initial block of the module. Each instruction is stored as a 32-bit value in the mem array.

The always block in the module is triggered whenever the address changes. It reads the 32-bit instruction stored in the mem array at the address specified by address, and assigns this instruction to the instruction output. This means that the instruction output will always contain the instruction stored at the memory address specified by address.

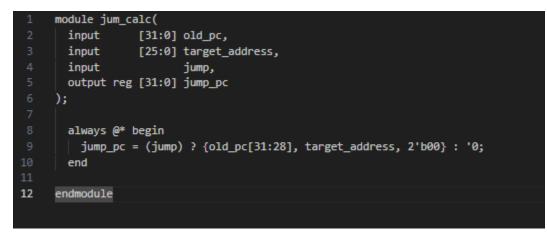

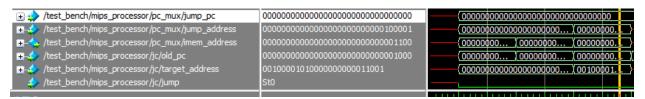

**JUMP CALCULATION:** Calculates the target jump address and determines whether the jump should be taken or not.

Figure 3.3.7: Jump calculation

The old\_pc input is the current address of the instruction being executed. The target\_address input is the 26-bit address of the instruction to which the program should jump. The jump input is a signal that determines whether the jump should be taken.

The jump\_pc output is the computed target address of the jump instruction. The module uses the jump signal to decide whether to take the jump or not. If the jump signal is asserted, the module constructs the jump address by concatenating the upper 4 bits of the current address (old\_pc[31:28]) with the 26-bit target address (target\_address) and appending 2 bits of zero (2'b00) to the least significant end. Otherwise, the module sets jump\_pc to zero.

**PROGRAM COUNTER:** The program\_counter module is responsible for keeping track of the program counter (PC) for a processor. The program counter is a register that stores the address of the current instruction being executed, and it is updated after each instruction is executed.

| 1  | module program_counter (          |                                                             |  |  |  |

|----|-----------------------------------|-------------------------------------------------------------|--|--|--|

| 2  | input clk,                        | // clock input (active-high)                                |  |  |  |

| З  | input reset,                      | // reset input (active-low)                                 |  |  |  |

| 4  | input [31:0] pc_in,               | <pre>// updated pc for the branch/jump instruction(s)</pre> |  |  |  |

| 5  | output reg [31:0] pc_adder,       | <pre>// pc of the next instruction to be executed</pre>     |  |  |  |

| 6  | output reg [31:0] pc_out          | <pre>// pc of the next instruction to be executed</pre>     |  |  |  |

| 7  | );                                |                                                             |  |  |  |

| 8  |                                   |                                                             |  |  |  |

| 9  | always @(posedge clk or nege      | edge reset) begin                                           |  |  |  |

| 10 | if (reset) begin                  |                                                             |  |  |  |

| 11 | pc_out <= 32'd0;                  |                                                             |  |  |  |

| 12 | end else begin                    |                                                             |  |  |  |

| 13 | <pre>pc_out &lt;= pc_in;</pre>    |                                                             |  |  |  |

| 14 | end                               |                                                             |  |  |  |

| 15 | end                               |                                                             |  |  |  |

| 16 |                                   |                                                             |  |  |  |

| 17 | always @* begin                   |                                                             |  |  |  |

| 18 | <pre>pc_adder = pc_out + 4;</pre> |                                                             |  |  |  |

| 19 | end                               |                                                             |  |  |  |

| 20 |                                   |                                                             |  |  |  |

| 21 | endmodule                         |                                                             |  |  |  |

Figure 3.3.8: Program counter

The module has four ports: clk, reset, pc\_in, pc\_adder, and pc\_out. clk is the clock signal for the processor, reset is the reset signal, pc\_in is the updated program counter value, pc\_adder is the program counter for the next instruction to be executed, and pc\_out is the program counter for the current instruction being executed.

The always @(posedge clk or negedge reset) block handles the clock and reset signals. When reset is active low, the pc\_out is set to 0. Otherwise, the pc\_out is set to the updated program counter value pc\_in during the positive edge of the clk signal.

The always @\* block is a combinational logic that calculates the pc\_adder value by adding 4 to pc\_out. This value is used to determine the address of the next instruction to be executed after the current instruction.

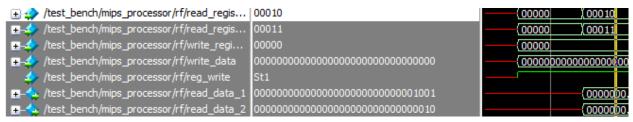

**REGISTER FILE:** A register file is a collection of registers that are used in a digital circuit to temporarily store and manipulate data during computation. The registers can be accessed by the circuit's control unit, which retrieves data from the registers, performs arithmetic or logical operations on the data, and stores the results back into the registers.

|    | module register_file (                                               |  |  |  |  |  |  |

|----|----------------------------------------------------------------------|--|--|--|--|--|--|

| 2  | input clk, // clock input (active-high)                              |  |  |  |  |  |  |

| 3  | input [4: 0] read_register_1,                                        |  |  |  |  |  |  |

| 4  | input [4: 0] read_register_2,                                        |  |  |  |  |  |  |

| 5  | input [4: 0] write_register,                                         |  |  |  |  |  |  |

| 6  | input [31:0] write_data,                                             |  |  |  |  |  |  |

| 7  | input reg_write,                                                     |  |  |  |  |  |  |

| 8  | output [31:0] read_data_1,                                           |  |  |  |  |  |  |

| 9  | output [31:0] read_data_2                                            |  |  |  |  |  |  |

| 10 | );                                                                   |  |  |  |  |  |  |

| 11 |                                                                      |  |  |  |  |  |  |

| 12 | reg [31:0] registers[0:31];                                          |  |  |  |  |  |  |

| 13 |                                                                      |  |  |  |  |  |  |

| 14 |                                                                      |  |  |  |  |  |  |

| 15 | <pre>// initial values of the registers (for testing purposes)</pre> |  |  |  |  |  |  |

| 16 | initial begin                                                        |  |  |  |  |  |  |

| 17 | registers [1] = 32'h2;                                               |  |  |  |  |  |  |

| 18 | registers [2] = 32'h2;                                               |  |  |  |  |  |  |

| 19 | registers [3] = 32'h3;                                               |  |  |  |  |  |  |

| 20 | registers [4] = 32'h5;                                               |  |  |  |  |  |  |

| 21 | registers [5] = 32'h5;                                               |  |  |  |  |  |  |

| 22 | end                                                                  |  |  |  |  |  |  |

| 23 |                                                                      |  |  |  |  |  |  |

| 24 | always @(posedge clk) begin                                          |  |  |  |  |  |  |

| 25 | if (reg_write) begin                                                 |  |  |  |  |  |  |

| 26 | <pre>registers[write_register] &lt;= write_data;</pre>               |  |  |  |  |  |  |

| 27 | end                                                                  |  |  |  |  |  |  |

| 28 | end                                                                  |  |  |  |  |  |  |

| 29 |                                                                      |  |  |  |  |  |  |

| 30 | <pre>assign read_data_1 = registers[read_register_1];</pre>          |  |  |  |  |  |  |

| 31 | assign read_data_2 = registers[read_register_2];                     |  |  |  |  |  |  |

| 32 |                                                                      |  |  |  |  |  |  |

| 33 | endmodule                                                            |  |  |  |  |  |  |

|    |                                                                      |  |  |  |  |  |  |

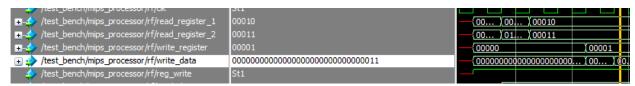

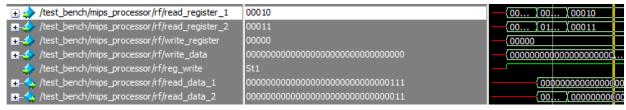

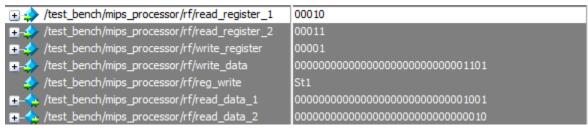

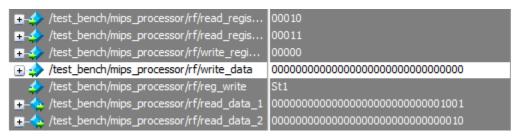

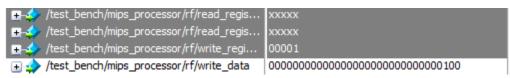

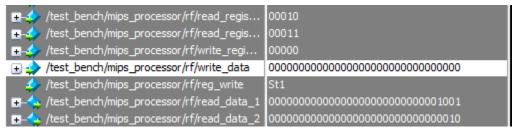

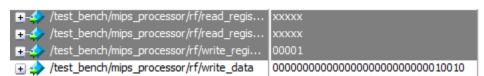

Figure 3.3.9: Register file

The module has the following inputs and outputs:

Inputs:

- clk: the clock input signal.

- read\_register\_1: a 5-bit input signal that specifies the first register to be read.

- read\_register\_2: a 5-bit input signal that specifies the second register to be read.

- write\_register: a 5-bit input signal that specifies the register to be written to.

- write\_data: a 32-bit input signal that specifies the data to be written to the register.

- reg\_write: an input signal that specifies whether the write operation is to be performed.

Outputs:

- read\_data\_1: a 32-bit output signal that contains the data read from the first register.

- read data 2: a 32-bit output signal that contains the data read from the second register.

The module contains a 32-bit array of registers called "registers", with one register for each of the 32 possible register addresses. The initial values of the registers are set in an "initial" block, which is used for testing purposes.

The "always" block is triggered by the positive edge of the clock signal. If the "reg\_write" signal is high, the data specified by the "write\_data" signal is written to the register specified by the "write\_register" signal.

The "assign" statements are used to assign the data read from the specified registers to the "read\_data\_1" and "read\_data\_2" output signals.

**REGISTER FILE MUX:** The reg\_file\_mux module is a multiplexer that selects the destination register for a write operation in a MIPS processor's register file based on the instruction being executed.

Figure 3.3.10: Register file mux

The module takes in a 32-bit instruction signal and a control signal reg\_dst. The reg\_dst signal determines which of two fields in the instruction contains the destination register number. If reg\_dst is high, then bits 20-16 of the instruction contain the register number, otherwise bits 15-11 are used. The module outputs the selected register number on a 5-bit signal mux output.

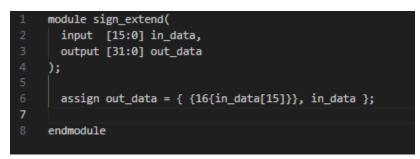

**SIGN EXTEND:** "sign\_extend" takes a 16-bit input "in\_data" and extends the sign bit (the leftmost bit) to fill the remaining 16 bits, creating a 32-bit output "out\_data".

Figure 3.3.11: Sign extend

The sign bit is typically used to indicate whether the number is positive or negative. If the sign bit is 0, the number is positive; if it is 1, the number is negative. In a two's complement system, the sign bit is also used to represent the magnitude of the number.

The code uses a concatenation operator ({ }) to create a 32-bit value. The first argument is an array of 16 copies of the sign bit (in\_data[15]), which is used to fill the upper 16 bits of the output. The second argument is the original 16-bit input (in\_data), which is used to fill the lower 16 bits of the output. The resulting 32-bit output is then assigned to "out\_data".

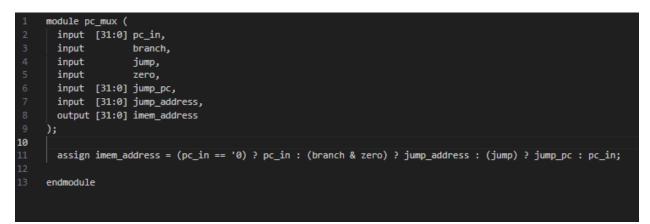

**PROGRAM COUNTER MUX:** PC (program counter) multiplexer selects the next program counter address. It has five inputs and one output.

Figure 3.3.12: PC Mux

The pc\_in input is the current program counter address, which is the address of the instruction to be executed next. The branch input indicates whether the current instruction is a branch instruction or not. The jump input indicates whether the current instruction is a jump instruction or not. The zero input is the result of the ALU's zero flag, which indicates whether the previous ALU operation resulted in a zero value. The jump\_pc input is the program counter value that should be used if the current instruction is a

jump instruction. The jump\_address input is the jump target address, which is computed based on the instruction's offset value.

The imem\_address output is the selected program counter address that should be used to fetch the next instruction. It is computed based on the current program counter address, branch condition, jump condition, and jump target address. If pc\_in is zero, the output is also set to zero. Otherwise, if the current instruction is a branch instruction and the zero flag is set, the output is set to the jump target address. If the current instruction is a jump instruction, the output is set to the jump program counter address. Otherwise, the output is set to the next sequential program counter address.

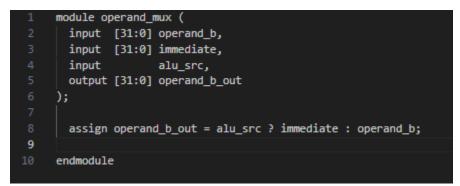

**OPERAND MUX:** Operand\_mux implements a multiplexer that selects between two input operands based on a control signal alu\_src. If alu\_src is high, then the output operand\_b\_out is set to the immediate value immediate, otherwise it is set to the value of the second input operand\_b. This multiplexer is typically used in a CPU's datapath to select between two sources of operands for an arithmetic or logical operation, depending on the instruction being executed.

Figure 3.3.13: Operand mux

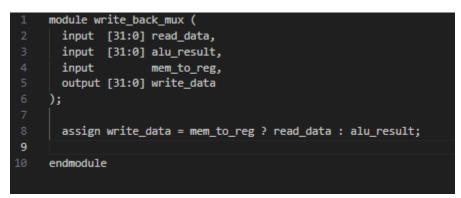

**WRITE BACK MUX:** This module implements a multiplexer (mux) used for selecting data to be written back to a register in a processor's write-back stage. The module has three inputs: read\_data, alu\_result, and mem\_to\_reg, and one output write\_data. The read\_data input represents the data read from memory in the memory access stage, alu\_result is the output of the arithmetic and logic unit (ALU) in the execution stage, and mem\_to\_reg is a control signal that determines whether the output of the memory access stage or the output of the ALU is selected for writing back to a register.

Figure 3.3.14: Write back mux

The write\_data output of the module is set to read\_data if mem\_to\_reg is asserted (i.e., is equal to 1), otherwise it is set to alu\_result. This mux is used to select the correct data to be written back to a register in a processor's write-back stage, depending on whether the instruction requires data from memory or the output of the ALU.

**CONTROL UNIT:** The control unit takes an instruction as input and generates various control signals based on the opcode and function fields of the instruction.

The module defines output signals for reg\_dst, branch, jump, mem\_read, mem\_to\_reg, alu\_op, mem\_write, alu\_src, and reg\_write. These signals are used to control other parts of the processor, such as the register file, ALU, and memory.

| 1  | module contro | ol_unit | (            |

|----|---------------|---------|--------------|

| 2  | input         | [31:0]  | instruction, |

| 3  | output reg    |         | reg_dst,     |

| 4  | output reg    |         | branch,      |

| 5  | output reg    |         | jump,        |

| 6  | output reg    |         | mem_read,    |

| 7  | output reg    |         | mem_to_reg,  |

| 8  | output reg    | [1: 0]  | alu_op,      |

| 9  | output reg    |         | mem_write,   |

| 10 | output reg    |         | alu_src,     |

| 11 | output reg    |         | reg_write    |

| 12 | );            |         |              |

| 13 |               |         |              |

Figure 3.3.15: Initialize

The control unit extracts the opcode field from the instruction and uses it to determine which instruction type it is dealing with: R-Type, I-Type, or J-Type. It then sets the control signals accordingly.

| <pre>// Extract the opcode and function fields from the instruction reg [5:0] opcode;</pre> |

|---------------------------------------------------------------------------------------------|

| <pre>// Shuffle unit always @* begin     opcode = instruction [31:26]; end</pre>            |

| // control signals for R, I and J-TYPE instructions                                         |

| always @* begin                                                                             |

| case (opcode)                                                                               |

| // R-Type                                                                                   |

| 6'b000000: begin                                                                            |

| reg_dst = 1'b0;                                                                             |

| branch = 1'b0;                                                                              |

| jump = 1'b0;                                                                                |

| <pre>mem_read = 1'b0;</pre>                                                                 |

| <pre>mem_to_reg = 1'b0;</pre>                                                               |

| alu_op = 2'b10;                                                                             |

| <pre>mem_write = 1'b0;</pre>                                                                |

| alu_src = 1'b0;                                                                             |

| reg_write = 1'b1;                                                                           |

| end                                                                                         |

Figure 3.3.16: R-type instruction

This part of the code is defining the values of various control signals based on the opcode field of the input instruction. These control signals are used to enable or disable various components of the processor during the execution of the instruction.

The case statement checks the value of the opcode variable and executes the corresponding code block. In this particular code block, which corresponds to R-Type instructions, the control signals are set as follows:

- reg\_dst: This signal indicates whether the instruction writes to a register or not. In this case, it is set to 0, indicating that the instruction does not write to a register.

- branch: This signal indicates whether the instruction is a branch instruction. In this case, it is set to 0, indicating that the instruction is not a branch instruction.

- jump: This signal indicates whether the instruction is a jump instruction. In this case, it is set to 0, indicating that the instruction is not a jump instruction.

- mem\_read: This signal indicates whether the instruction performs a memory read operation. In this case, it is set to 0, indicating that the instruction does not perform a memory read operation.

- mem\_to\_reg: This signal indicates whether the data read from memory should be written to a register or not. In this case, it is set to 0, indicating that the data should not be written to a register.

- alu\_op: This signal indicates the operation that should be performed by the ALU. In this case, it is set to 2'b10, indicating that the ALU should perform a subtraction operation.

- mem\_write: This signal indicates whether the instruction performs a memory write operation. In this case, it is set to 0, indicating that the instruction does not perform a memory write operation.

- alu\_src: This signal indicates whether the second operand of the ALU should come from the immediate field or the second register file. In this case, it is set to 0, indicating that the second operand should come from the second register file.

- reg\_write: This signal indicates whether the instruction writes to a register or not. In this case, it is set to 1, indicating that the instruction writes to a register.

| // I-Type                                                                                                                                                                                              | 6'b100011: begin // LW                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6'b001000: begin // ADDI                                                                                                                                                                               | reg_dst = 1'b1;                                                                                                                                                                                        |

| <pre>reg_dst = 1'b1;<br/>branch = 1'b0;<br/>jump = 1'b0;<br/>mem_read = 1'b0;<br/>mem_to_reg = 1'b0;<br/>alu_op = 2'b00;<br/>mem_write = 1'b0;<br/>alu_src = 1'b1;<br/>reg_write = 1'b1;</pre>         | <pre>branch = 1'b0;<br/>jump = 1'b0;<br/>mem_read = 1'b1;<br/>mem_to_reg = 1'b1;<br/>alu_op = 2'b00;<br/>mem_write = 1'b0;<br/>alu_src = 1'b1;<br/>reg_write = 1'b1;</pre>                             |

| end                                                                                                                                                                                                    | end<br>6'b101011: begin // SW                                                                                                                                                                          |

| 6'b000100: begin // BEQ<br>reg_dst = 1'b0;<br>branch = 1'b1;<br>jump = 1'b0;<br>mem_read = 1'b0;<br>mem_to_reg = 1'b0;<br>alu_op = 2'b01;<br>mem_write = 1'b0;<br>alu_src = 1'b0;<br>reg_write = 1'b0; | <pre>reg_dst = 1'b1;<br/>branch = 1'b0;<br/>jump = 1'b0;<br/>mem_read = 1'b0;<br/>mem_to_reg = 1'b0;<br/>alu_op = 2'b00;<br/>mem_write = 1'b1;<br/>alu_src = 1'b1;<br/>reg_write = 1'b0;<br/>end</pre> |

| end                                                                                                                                                                                                    | enu                                                                                                                                                                                                    |

Figure 3.3.17: I-type instruction

This is a block of code within the always block that assigns control signals to various outputs based on the value of the opcode signal, which determines the type of instruction being executed.

For example the BEQ instructions, the code sets the following signals:

- reg\_dst to 1'b0, indicating that this instruction does not specify a destination register

- branch to 1'b1, indicating that this instruction is a branch instruction

- jump to 1'b0, indicating that this instruction is not a jump instruction

- mem\_read to 1'b0, indicating that this instruction does not read from memory

- mem to reg to 1'b0, indicating that this instruction does not write to memory

- alu op to 2'b01, indicating that the ALU operation for this instruction is subtraction

- mem write to 1'b0, indicating that this instruction does not write to memory

- alu\_src to 1'b0, indicating that the second operand of the ALU operation comes from the register file

- reg\_write to 1'b0, indicating that this instruction does not write to a register.

**PROCESSOR TOP MODULE:** This module is an implementation of a processor's datapath, containing several sub-modules for the various stages of the processor's operation, such as instruction fetch, decode, execute, and memory access. Each sub-module is set to be interconnected using several input and output wires, which are used to pass data and control signals between modules.

Here are some of the key sub-modules and wires in this design:

- PC Selection MUX: selects between the output of the branch adder, jump calculator, and instruction memory to determine the next address to fetch from

- Program Counter: generates the next address to fetch from, based on the output of the PC Selection MUX

- Instruction Memory: reads the instruction at the current address specified by the Program Counter

- Control Unit: decodes the instruction and generates control signals for the rest of the datapath, such as whether to read from or write to memory or registers

- Register File MUX: selects between the destination register specified by the instruction and a register specified by the Control Unit

- Register File: reads from or writes to the register file based on the input signals

- ALU Control Unit: generates the appropriate ALU operation based on the instruction and control signals

- Sign Extend: extends the immediate value in the instruction to a full 32-bit value

- Branch Adder: computes the branch address based on the current PC and the sign-extended immediate value in the instruction

- Jump Calculator: computes the jump address based on the current PC and the immediate value in the instruction

In summary, all of the modules that had been created so far for the single-cycle processor, come all together and get wired in this module to be interconnected with one another to pass the data, address, and values generated by the instructions.

#### **3.3.2.** Task 2: Implementation of Forwarding logic to transform into pipeline logic

1. Since the single-cycle MIPS processor from task 1, we will go ahead and implement the forwarding logic by implementing the following modules:

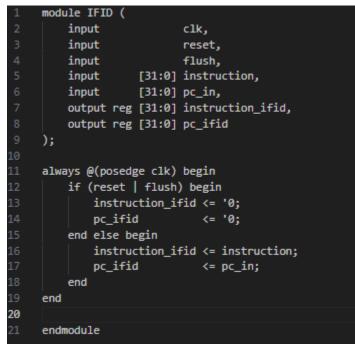

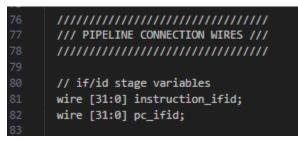

**IF\_ID MODULE:** This module is responsible for storing the fetched instruction and its associated program counter value in registers so that they can be passed to the next stage of the pipeline.

Figure 3.3.18: IF/ID Module

The inputs to the module are clk, reset, flush, instruction, and pc\_in. The clk input is a clock signal that is used to synchronize the operations of the module. The reset and flush inputs are used to reset and flush the pipeline, respectively. The instruction input is the 32-bit instruction fetched from memory, and the pc in input is the program counter value associated with the fetched instruction.

The module has two outputs: instruction\_ifid and pc\_ifid. These are both 32-bit registers that store the instruction and program counter values, respectively, in the instruction fetch/decode stage of the pipeline.

The module uses an always block that triggers on the positive edge of the clk signal. If either the reset or flush inputs are asserted, the registers are reset to zero. Otherwise, the values of instruction and pc\_in are loaded into instruction\_ifid and pc\_ifid, respectively.

**ID\_EX MODULE:** The IDEX stage takes the instruction fetched in the Instruction Fetch stage and decodes it, preparing it for execution in the Execute stage.

| 4  |               |        |                             |

|----|---------------|--------|-----------------------------|

|    | module IDEX ( |        |                             |

| 2  | input         |        | clk,                        |

| 3  | input         |        | reset,                      |

| 4  | input         |        | flush,                      |

| 5  | input         |        | reg_dst,                    |

| 6  | input         |        | branch,                     |

| 7  | input         |        | jump,                       |

| 8  | input         |        | mem_read,                   |

| 9  | input         |        | mem_to_reg,                 |

| 10 | input         | [1: 0] | alu_op,                     |

| 11 | input         |        | mem_write,                  |

| 12 | input         |        | alu_src,                    |

| 13 | input         |        | reg_write,                  |

| 14 | input         | [31:0] | operand_a,                  |

| 15 | input         | [31:0] | operand_b,                  |

| 16 | input         | [31:0] | instruction_ifid,           |

| 17 | input         | [31:0] | pc_ifid,                    |

| 18 | input         | [4: 0] | wb_address,                 |

| 19 | output reg    |        | <pre>reg_dst_idex,</pre>    |

| 20 | output reg    |        | branch_idex,                |

| 21 | output reg    |        | jump_idex,                  |

| 22 | output reg    |        | mem_read_idex,              |

| 23 | output reg    |        | <pre>mem_to_reg_idex,</pre> |

| 24 | output reg    | [1: 0] | alu_op_idex,                |

| 25 | output reg    |        | <pre>mem_write_idex,</pre>  |

| 26 | output reg    |        | alu_src_idex,               |

| 27 | output reg    |        | <pre>reg_write_idex,</pre>  |

| 28 | output reg    | [31:0] | operand_a_idex,             |

| 29 | output reg    | [31:0] | operand_b_idex,             |

| 30 | output reg    | [31:0] | instruction_idex,           |

| 31 | output reg    | [31:0] | pc_idex,                    |

| 32 | output reg    | [4: 0] | wb_address_idex             |

| 33 | );            |        |                             |

|    |               |        |                             |

Figure 3.3.19: IDEX initialization

The module takes several input signals representing various control signals and data from the IFID stage and provides the necessary control signals and data for the Execute stage. The inputs include clk for the clock, reset for reset, flush to clear the pipeline in case of a branch misprediction, instruction\_ifid and pc\_ifid to receive instruction and program counter from the previous stage, and operand\_a and operand\_b to receive data from the register file, among others.

The output signals are derived from the inputs after some computations and include instruction\_idex which carries the decoded instruction, pc\_idex which carries the program counter for the current instruction, and operand\_a\_idex and operand\_b\_idex which carry the operands for the current instruction. Other output signals include various control signals for

execution such as reg\_write\_idex, mem\_read\_idex, mem\_write\_idex, and alu\_op\_idex, among others.

```

always @(posedge clk) begin

if (reset | flush) begin

reg_dst_idex <= '0;</pre>

branch_idex

<= '0;

jump_idex

<= '0;

mem_read_idex <= '0;</pre>

mem_to_reg_idex <= '0;</pre>

alu_op_idex

<= '0;

mem_write_idex <= '0;</pre>

alu_src_idex

<= '0;

reg_write_idex <= '0;</pre>

operand_a_idex <= '0;</pre>

operand_b_idex <= '0;</pre>

instruction_idex <= '0;</pre>

pc_idex

<= '0;

wb_address_idex <= '0;</pre>

end else begin

reg_dst_idex

<= reg_dst;

branch_idex

<= branch;

jump_idex

<= jump;

mem_read_idex

<= mem_read;

mem_to_reg_idex <= mem_to_reg;</pre>

alu_op_idex

<= alu_op;

mem_write_idex <= mem_write;</pre>

alu_src_idex <= alu_src;</pre>

reg_write_idex <= reg_write;</pre>

operand_a_idex <= operand_a;</pre>

operand_b_idex <= operand_b;</pre>

instruction_idex <= instruction_ifid;</pre>

<= pc_ifid;

pc_idex

wb_address_idex <= wb_address;</pre>

end

end

```

Figure 3.3.20: IDEX always module

**EX\_MEM MODULE:** The EXMEM module is a module that represents a stage in a pipelined processor. Specifically, this module represents the execution-to-memory stage of the pipeline, where results from the execution stage are written to the memory stage.

| 1                                                      | module EXMEM ( |        |                    |

|--------------------------------------------------------|----------------|--------|--------------------|

| 2                                                      | input          |        | clk,               |

|                                                        | input          |        | reset,             |

| 4                                                      | input          |        | reg_dst_idex,      |

| 5                                                      | input          |        | branch_idex,       |

| 3<br>4<br>5<br>6<br>7                                  | input          |        | jump_idex,         |

| 7                                                      | input          |        | mem_read_idex,     |

| 8                                                      | input          |        | mem_to_reg_idex,   |

| 9                                                      | input          |        | alu_op_idex,       |

| .0                                                     | input          |        | mem_write_idex,    |

| .1                                                     | input          | [1: 0] | alu_src_idex,      |

| .2                                                     | input          |        | reg_write_idex,    |

| 8<br>9<br>.0<br>.1<br>.2<br>.3<br>.4<br>.5<br>.6<br>.7 | input          | [31:0] | operand_a_idex,    |

| .4                                                     | input          | [31:0] | operand_b_idex,    |

| .5                                                     | input          | [31:0] | instruction_idex,  |

| .6                                                     | input          | [31:0] | alu_result,        |

|                                                        | input          |        | zero,              |

| .8                                                     | input          | [31:0] | pc_idex,           |